High quality. Cost effective. On time.

We combine a deep knowledge of hardware design verification domain, languages, methodologies and tools with extensive project experience to help companies deliver complex designs on time and within budget and infrastructure constraints.

Our consulting services range from functional and system-level verification to training and outsourcing. We provide services either on-site, at the client’s location, or off-site, and we are constantly striving to meet our clients’ communication and cost requirements.

Since the company was established in 2003, we have built up a solid base of expertise in pre-silicon hardware verification and a strong reputation among our clients in the automotive, telecommunications, and computers and peripherals industries.

About Pre-Silicon Verification Domain

The semiconductor industry focuses on the design and production of integrated circuits (ICs), which is one of the most complex fabrication processes in the history of humankind. The technological advancements in semiconductors are reflected in many other industries in one form or another, including the semiconductor industry itself. There are plenty of examples where the semiconductor industry produces ICs at the heart of dream-come-true products, services or endeavors: mobile communications and computing, GPS navigation, electrical cars and green technologies, drones and self-driving vehicles, telemedicine, smart prostetics, smart health trackers, artificial intelligence, smart cities, smart farming, Mars exploration, and more.

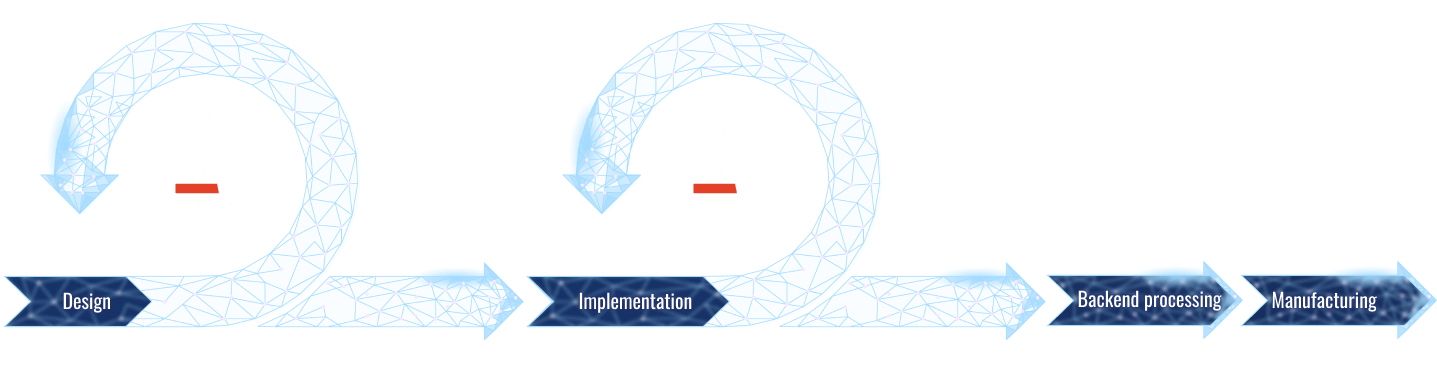

The semiconductor industry has enabled the development of smart and green technologies that, together with public opinion, incentivises politicians to vote for almost impossible emissions targets and agree on courageous environmental policies. However, all the positive impact on daily lives and future humankind evolution comes with associated costs and risks that are spread along the IC design, implementation and production chain. The IC production process consists in 4 stages: design, implementation, backend processing, and manufacturing. The costs and risks have to be mitigated at every stage of the process since their impact increases non-linearly as it gets closer to the end of the production line.

All (functional, performance, and architectural) defects (bugs) must be found, fixed, and verified in the first 3 stages since the manufacturing is completely automated, and it runs based on the results of the backend processing stage. Correcting functional or performance defects during the manufacturing stage is almost impossible, both technologically and financially. The costs of restarting the IC manufacturing process for a “respin” are prohibitive. Although there is a sequential relationship between the 4 stages, modern agile development methodologies (e.g., Scrum, KanBan, and XP) enable projects to run them in an iterative, quasi-parallel way. This has two immediate benefits: it reduces the time to market, and it reduces the defect turn-around time via the flexibility to fix bugs early in the process. AMIQ has a long history of promoting and ramping up agile silicon development.

DESIGN PHASES

In the design phase, IC stakeholders (such as end users, software and hardware architects, designers, and verification engineers) define the interfaces, functionality, performance, and architecture.

The result is a high-level definition (typically a Word document) that will be further refined by IC design and verification engineers. As with any human endeavor, there is always the possibility of mistakes: IC specifications omit some functionality descriptions, use case configurations don’t reflect the desired behavior, configuration parameters have the wrong value domains, descriptions of interacting functionalities do not agree, data frames descriptions do not match the protocol bandwidth, etc. Engineers put a lot of effort into reviewing and correcting the specifications. This process spans the whole design cycle of the IC, from day zero to tape-out (the final release sent to manufacturing).

In this stage, AMIQ engineers contribute by reviewing IC design specifications, proposing verification strategies, designing verification environment architectures, and assessing the verification requirements and effort. The architecture team gets early feedback on the specification alignment/quality and the verifiability/testability of the IC implementation. Equally important, the project management gets an early estimation of the verification effort and schedule (which usually consumes more than 70% of the IC design and implementation stages).

In the implementation stage, the IC design engineers translate IC specifications into an implementation using a register-transfer-level (RTL) design language (SystemVerilog, VHDL, or SystemC), which is executable code that can be simulated and verified. The IC design engineers translate the IC specification to the best of their understanding and technical abilities, which is a nice way to say there is still room for human errors. That is why, as IC complexity increased, a new position was introduced: the verification engineer, a critical role in the success of any IC project.

The verification engineer must prove the IC is implemented according to the IC specification by using specific tools, hardware verification languages (HVLs) such as e-Language and SystemVerilog, and supporting methodologies. The verification engineer reviews the IC specifications, proposes a verification plan (a set of verification metrics that must be collected during the verification process), and implements an HVL verification environment that will exercise the functionality, measure the performance, and collect the verification metrics. The results of the IC verification are usually specification issues, implementation bugs, and a verification report that presents and explains the collected verification metrics (code coverage, functional coverage, scenario coverage, coverage holes, pass rate, performance, etc.). AMIQ services are fully deployed in this stage, from verification metrics definition to verification environment implementation to verification closure to final verification sign-off.

The backend processing takes in the RTL implementation and synthesizes the required files for the IC layout. At this stage the netlist is synthesized, clock trees are added, scan chains are inserted, floor planning is determined, and the design is placed, routed, and optimized to obey the area constraints and to pass static timing analysis checks. After the final layout is verified, the files can be sent to manufacturing.

In the final stage the IC design company commissions the production of ICs by a semiconductor foundry, which sets up the production process, produces the ICs, tests, packages, and ships them. The IC is, more or less, written in stone (well, in silicon) and there is not much left to do if design or implementation bugs are found except for a very expensive re-spin that would delay time to market for the IC. That is why it is crucial to find as many of the bugs as possible before this stage, and this is AMIQ’s area of expertise.

Expert Verification Services

Since the company was established in 2003, we have built up a solid base of expertise in pre-silicon hardware verification and a strong reputation among our clients in the automotive, telecommunications, and computers and peripherals industries.

Functional verification is the process of demonstrating the functional correctness of a design with respect to the design specifications. Functional verification does not confirm the correctness of the design specification and assumes that the design specification is correct. It is one of the most challenging steps of the IC design cycle, and is the main reason for IC re-spin.

We provide ASIC and FPGA functional verification services spanning the entire coverage-driven verification flow from specification to coverage sign-off. Our consultants have the expertise to work on an entirely new verification project from beginning to end, as well as the skills and flexibility to engage with a client at any critical point in an IC project.

We have extensive experience of all major hardware verification languages (HVLs) such as e-Language and SystemVerilog, and methodologies such as UVM, OVM, VMM, and e RM.

We are proficient in the use of all major EDA vendor tools, such as Cadence Incisive® Enterprise Simulator, the Synopsys VCS® functional verification solution, and Mentor’s Questa® Advanced Simulator. We also use the Cadence Palladium® series of accelerators/emulators, system-level modeling languages such as SystemC, and tools like MATLAB®.

The AMIQ team is also able to help clients with verification project management and third-party EDA vendor communication, including requirements specification and issue handling.

Due to the very high clock cycle consumption of system-level verification, the planning and implementation of the verification process needs to be done carefully. The verification process requires in-depth planning, advanced verification skills such as object-oriented language programming (SystemVerilog, C++/SystemC), methodology awareness (UVM), and a creative approach to problem solving.

We have the expertise to provide system-level verification services for complex SoCs, involving working with various hardware and software IPs and using specific tools such as hardware acceleration and hardware emulation.

Our experience with System Level Verification spans an extensive technical skills matrix, including:

- e-Language, SystemVerilog, SystemVerilog Assertions (SVA) and C/C++

- Simulation and hardware emulation

- Directed tests or randomized user cases

- Mixing e/SystemVerilog and C/C++ to create self-checking tests

- Using e/SystemVerilog or TLM/SystemC/MATLAB models as a golden model

- Designing and implementing the TBA-ready drivers or monitors

- Formal verification

- Integrating the subsystem verification environment

- Elevating coverage definitions from block level to system level

- Porting tests from lower integration levels to the top level

- Porting system-level environments to vanilla versions for derivative SoCs

- Developing automation tools or debug-effort decreasing tools

We also have experience of System Level Verification management, including:

- Verification plan design

- Leading verification planning sessions with cross-functional teams to increase the quality of the verification and shorten sign-off time

- Third-party vendor communication management

- Subsystem verification environment reuse audit

- Subsystem coverage reuse

We have been successful at rescuing projects that have gone off track. We start by identifying the project bottlenecks. We then define a rescue strategy and implement it. We analyze performance periodically and continue to refine our strategy, taking into account all internal and external factors, until the project is back on track.

Our ramp-up services include infrastructure setup, template creation, methodology/flow definition and implementation, and resource planning. We can also perform interviews to assist with hiring new team members.

We can develop verification IPs (VIPs) on demand, for any protocol or function, by using any one of the HVLs (e, SystemVerilog) or assertion languages (SVA, PSL).

Normally, the client provides us with the protocol or function specification and we deliver the code, documentation, suites of tests, regression reports, and scripts. The deliverables are prioritized according to the client’s requirements and scheduled in such a way that the integration work can start before the final release of the VIP.

Furthermore, AMIQ consultants can provide VIP integration and maintenance support.

We provide VIP qualification services that aim to ensure a VIP is functionally compliant with the protocol/functional specification, has generation capabilities that cover all required scenarios, contains correct checkers, and includes relevant coverage items. We also verify that the architecture and implementation is compliant with a specific methodology, such as UVM.

AMIQ has accumulated an extensive verification expertise that spans across technologies, projects, companies and cultures. AMIQ can deploy this expertise in the form of a specialized training that is tailored based on the project requirements, available technologies/infrastructure and students skills. Compared to the classic, academic-like, verification courses, the AMIQ training is fully integrated with the project in which the students will deliver value from the first day. The senior consultants will teach the verification technologies, apply agile methodologies and mentor the students to enable them grow into knowledgeable, self-reliant and proactive verification engineers.

Ramp-up

Functional Verification

Functional verification is the process of demonstrating the functional correctness of a design with respect to the design specifications. Functional verification does not confirm the correctness of the design specification and assumes that the design specification is correct. It is one of the most challenging steps of the IC design cycle, and is the main reason for IC re-spin.

We provide ASIC and FPGA functional verification services spanning the entire coverage-driven verification flow from specification to coverage sign-off. Our consultants have the expertise to work on an entirely new verification project from beginning to end, as well as the skills and flexibility to engage with a client at any critical point in an IC project.

We have extensive experience of all major hardware verification languages (HVLs) such as e-Language and SystemVerilog, and methodologies such as UVM, OVM, VMM, and e RM.

We are proficient in the use of all major EDA vendor tools, such as Cadence Incisive® Enterprise Simulator, the Synopsys VCS® functional verification solution, and Mentor’s Questa® Advanced Simulator. We also use the Cadence Palladium® series of accelerators/emulators, system-level modeling languages such as SystemC, and tools like MATLAB®.

The AMIQ team is also able to help clients with verification project management and third-party EDA vendor communication, including requirements specification and issue handling.

System Level Verification

Due to the very high clock cycle consumption of system-level verification, the planning and implementation of the verification process needs to be done carefully. The verification process requires in-depth planning, advanced verification skills such as object-oriented language programming (SystemVerilog, C++/SystemC), methodology awareness (UVM), and a creative approach to problem solving.

We have the expertise to provide system-level verification services for complex SoCs, involving working with various hardware and software IPs and using specific tools such as hardware acceleration and hardware emulation.

Ramp-up

Project Rescue and Ramp-up

We have been successful at rescuing projects that have gone off track. We start by identifying the project bottlenecks. We then define a rescue strategy and implement it. We analyze performance periodically and continue to refine our strategy taking into account all internal and external factors until the project is back on track.

Our ramp-up services include infrastructure setup, template creation, methodology/flow definition and implementation, and resource planning. We can also perform interviews to assist with hiring new team members.

Verification IP Development and Qualification

We can develop verification IPs (VIPs) on demand, for any protocol or function, by using any one of the HVLs (e, SystemVerilog) or assertion languages (SVA, PSL).

Normally, the client provides us with the protocol or function specification and we deliver the code, documentation, suites of tests, regression reports, and scripts. The deliverables are prioritized according to client’s requirements and schedule in such a way that the integration work can start before the final release of the VIP.

Furthermore, our consultants can provide VIP integration and maintenance support.

We provide VIP qualification services that aim to ensure a VIP is functionally compliant with the protocol/functional specification, has generation capabilities that cover all required scenarios, contains correct checkers and includes relevant coverage items. We also verify that the architecture and implementation is compliant with a specific methodology, such as UVM.

Coaching

We provide on-site and off-site training services for a broad range of hardware verification languages and methodologies. The training is delivered by senior consultants with comprehensive experience of working on a range of different projects with top companies.

Subscribe to our newsletter

Do you want to be up to date with our latest articles?